A pocos meses de la llegada del ‘Ivy Bridge’ Tri-Gate de Intel, investigadores de Harvard y Purdue presentan un dispositivo basado en transistores que conjugan una estructura en 3D y materiales semiconductores alternativos al silicio.

Las dos grandes tendencias en materia de chips por las que industria y comunidad científica avanzan hacia la miniaturización del silicio podrían confluir en un solo dispositivo. Esa es la promesa de un equipo de investigadores de las universidades de Harvard y Purdue que presentó en el Encuentro Internacional de Dispositivos Electrónicos (IEDM, celebrado en diciembre en Estados Unidos) una propuesta que integra el uso de nuevos materiales en los canales por los que circulan las cargas dentro de los transistores con la utilización de estructuras tridimensionales que mejoran la electrostática, permiten controlar mejor su tránsito y minimizan los escapes de carga que se acentúan con medidas inferiores a 22 nanómetros.

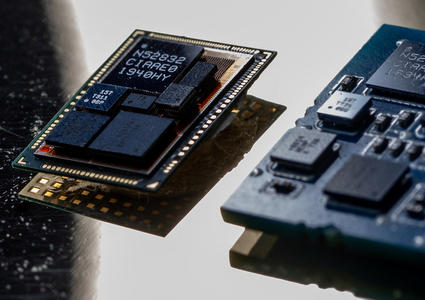

Los transistores presentados por estos científicos están formados por unos cables nanoscópicos que no están hechos de silicio, sino de otros semiconductores: arseniuro de indio y galio sobre un sustrato de fosfuro de indio, revestidos de óxido de aluminio. El dispositivo se ha creado utilizando el método ’top-down‘, en el que los nanocables son generados mediante el grabado fotolitográfico de las obleas de material semiconductor, en oposición al sistema ’bottom-up‘, donde el material se autoensambla 'de abajo a arriba’ para formar las estructuras.

Peide Ye, coordinador del trabajo que ha dado lugar a este sistema y profesor de la Escuela de Ingeniería Eléctrica y Computación de la Universidad de Purdue (EE.UU.), afirma que es “compatible con los procesos de fabricación convencionales”, lo que podría facilitar la adopción por parte de la industria de estos dispositivos tridimensionales.

El uso de materiales semiconductores alternativos al silicio para aumentar el rendimiento, y el uso de una estructura tridimensional para reducir la potencia, son dos caminos generalmente independientes que en este caso convergen en la propuesta de los investigadores. Sin embargo, pese a lo prometedor del avance, esta tecnología tendrá que superar aún importantes retos técnicos y económicos antes de poder incorporarse a nuestros móviles u ordenadores portátiles.

Los materiales semiconductores llevan décadas utilizándose para la creación de microprocesadores, memorias, circuitos y todo tipo de componentes electrónicos. Entre ellos, el silicio ha destacado siempre, debido a su abundancia y disponibilidad. Aunque aún es un material tecnológicamente vigente, otros semiconductores combinados en diferentes aleaciones e integrados en los futuros transistores están llamados a complementar sus ventajas y a facilitar los saltos a nuevos nodos tecnológicos. Las nuevas generaciones de chips se caracterizan por un tamaño cada vez más reducido de sus componentes y una mayor movilidad de las cargas eléctricas a través de ellos, lo que aumenta la velocidad de los dispositivos que los emplean.

Hace diez años, los ordenadores funcionaban con procesadores de 130 nanómetros que hoy día se han reducido a 32 o incluso a 22 nanómetros, si se cumple el anuncio de Intel de poner a la venta sus procesadores Ivy Bridge Tri-Gate en abril de este año. Estos procesadores integran millones de transistores que, en lugar de una estructura planar convencional, presentan una en 3D, al igual que los del equipo de Ye. La diferencia estriba en que estos últimos se han basado en nanotubos para desarrollarla, en lugar de en una estructura en forma de ‘aleta’ como la de Intel.

Hoy en día, sin embargo, los transistores más corrientes en circuitos digitales y analógicos siguen siendo los de estructura planar, que funcionan permitiendo o impidiendo el paso de la corriente como si de un interruptor se tratase. Estos, a su vez, incluyen dos tipos de transistores complementarios para contribuir al paso de la corriente: los ‘tipo n’, en los que los conductores de corriente son electrones, y los ‘tipo p’, en los que los conductores son huecos (cargas eléctricas positiva generadas por la ausencia de electrones).

En este caso, el equipo liderado por Ye no solo ha demostrado que es posible reducir la longitud de la puerta de sus transistores de estructura tridimensional hasta los 50 nanómetros -controlando con éxito los indeseados efectos de canal corto-, sino que, gracias a la miniaturización, ha conseguido al mismo tiempo incrementar la corriente que transporta electrones entre los nodos del circuito. Sin embargo, tal y como señala Francisco Gámiz, catedrático del departamento de Electrónica y Tecnología de Computadores de la Universidad de Granada, los huecos siguen siendo su asignatura pendiente, ya que este dispositivo “es solo conductor de electrones, es decir, carece de canal p”. Además, en el caso de construir uno que sí tuviera ambos canales, se generaría un desequilibrio de prestaciones en su conjunto, ya que los huecos no consiguen mejores velocidades en los materiales que ellos usan que en el silicio.

Gámiz observa también que el revestimiento de óxido de aluminio de este dispositivo es muy grueso, lo cual supone una desventaja adicional. “Dicen que podrían reducirlo, pero habría que comprobarlo", afirma el catedrático.

Otro de los grandes inconvenientes de estos transistores es la ausencia de una “crucial” integración en un sustrato de silicio, ya que, por el momento, se ha utilizado uno de fosfuro de indio “irrealmente caro” e inviable para su fabricación masiva, según explica Karol Kalna, profesor en la Universidad de Swansea (Reino Unido) e investigador en el Consejo Británico de Investigación en Ingeniería y Física. Kalna advierte de que “algunas áreas necesitan mejoras drásticas antes de que este dispositivo pueda retar a la tecnología de canales de silicio”.

El problema de la integración en silicio ya lo han abordado otros investigadores, como los que han trabajado en el proyecto europeo Duallogic. Su propuesta para solucionarlo consiste en utilizar diferentes materiales para cada uno de los dos tipos de transistores con el fin de mejorar la movilidad por separado y, finalmente, integrar ambos sobre la misma oblea de silicio. Este planteamiento, ideal en la teoría, aún no ha podido ser reproducido por los investigadores de Purdue y Harvard en su modelo experimental.

Como alternativa a las vías que apuestan por la estructura tridimensional de los transistores o a propuestas como la del equipo de Ye, varios centros de investigación europeos (Leti en Francia, Imec en Bélgica y Fraunhofer en Alemania), con el apoyo de grandes fabricantes como AMD e IBM, han impulsado una tecnología planar en 2D llamada SOI (en inglés, Silicon On Insulator) que ha conseguido reducir los transistores a longitudes de hasta 8 nanómetros en dispositivos aislados. Según Paul Boudre, director de operaciones de Soitec, fabricante de semiconductores para la industria electrónica y energética, esta tecnología está lista para llevar este año al mercado chips de 28 nanómetros.

“La tecnología SOI mejora las limitaciones de escalado que tienen las tecnologías de silicio convencionales”, afirma Gámiz. “Es una apuesta madura que, sin embargo, está encontrando una gran oposición por parte de algunos fabricantes como Intel porque desconfían de que alguien pueda garantizarles un suministro suficiente de obleas”.

Kalna, sin embargo, cree que el camino idóneo para superar los problemas de limitación de velocidad y disipación de potencia observados en las soluciones basadas en silicio es el de las arquitecturas tridimensionales. “Es realmente esperanzador que la investigación en materiales alternativos para los canales se mueva de forma decidida hacia arquitecturas no planares”, afirma en referencia al trabajo del equipo de Ye. “Las arquitecturas 3D serán necesarias inevitablemente en las tecnologías por debajo de los 22 nanómetros”, añade Kalna.

Solo el tiempo y el éxito o fracaso de productos como el Ivy Bridge dirán si 2012 es el año de los chips 3D, del afianzamiento de los SOI ultrafinos o el del avance de planteamientos eclécticos como el del equipo de Ye. Lo que sí está claro es que el futuro de la innovación electrónica pasa por el nacimiento de propuestas que no solo mejoren tecnologías y dispositivos, sino que perfeccionen también circuitos y sistemas.